## Low Power HART Modem

## AD5700/AD5700-1

# **Data Sheet**

**FEATURES**

HART-compliant fully integrated FSK modem 1200 Hz and 2200 Hz sinusoidal shift frequencies 115 uA maximum supply current in receive mode Suitable for intrinsically safe applications Integrated receive band-pass filter

Minimal external components required

Clocking optimized for various system configurations Ultralow power crystal oscillator (60 µA maximum) **External CMOS clock source**

Precision internal oscillator (AD5700-1only)

Buffered HART output—extra drive capability 8 kV HBM ESD rating

1.71 V to 5.5 V power supply

1.71 V to 5.5 V interface

-40°C to +125°C operation

4 mm × 4 mm LFCSP package

**HART** physical layer compliant

**UART** interface

#### **APPLICATIONS**

**Field transmitters HART multiplexers** PLC and DCS analog I/O modules **HART network connectivity**

#### GENERAL DESCRIPTION

The AD5700/AD5700-1 are single-chip solutions, designed and specified to operate as a HART® FSK half-duplex modem, complying with the HART physical layer requirements. The AD5700/AD5700-1 integrate all of the necessary filtering, signal detection, modulating, demodulating and signal generation functions, thus requiring few external components. The 0.5% precision internal oscillator on the AD5700-1 greatly reduces the board space requirements, making it ideal for line-powered applications in both master and slave configurations. The maximum supply current consumption is 115 µA, making the AD5700/ AD5700-1 an optimal choice for low power loop-powered applications. Transmit waveforms are phase continuous 1200 Hz and 2200 Hz sinusoids. The AD5700/AD5700-1 contain accurate carrier detect circuitry and use a standard UART interface.

**Table 1. Related Products**

| Part No. | Description                                                                                                        |

|----------|--------------------------------------------------------------------------------------------------------------------|

| AD5755-1 | Quad-channel, 16-bit, serial input, 4 mA to 20 mA and voltage output DAC, dynamic power control, HART connectivity |

| AD5421   | 16-bit, serial input, loop powered, 4 mA to 20 mA DAC                                                              |

| AD5410/  | Single-channel, 12-bit/16-bit, serial input, 4 mA to 20 mA                                                         |

| AD5420   | current source DACs                                                                                                |

| AD5412/  | Single-channel, 12-bit/16-bit, serial input, current                                                               |

| AD5422   | source and voltage output DACs                                                                                     |

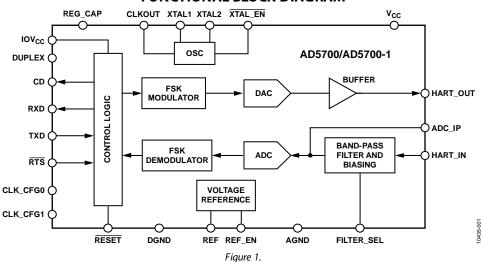

#### FUNCTIONAL BLOCK DIAGRAM

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners

| TABLE OF CONTENTS                                                                                     |                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Features                                                                                              | FSK Modulator                                                                                                                      |

| Applications1                                                                                         | Connecting to HART_OUT                                                                                                             |

| General Description1                                                                                  | FSK Demodulator                                                                                                                    |

| Functional Block Diagram1                                                                             | Connecting to HART_IN or ADC_IP                                                                                                    |

| Revision History                                                                                      | Clock Configuration                                                                                                                |

| Specifications                                                                                        | Supply Current Calculations                                                                                                        |

| Timing Characteristics                                                                                | Power-Down Mode                                                                                                                    |

| -                                                                                                     |                                                                                                                                    |

| Absolute Maximum Ratings6                                                                             | Full Duplex Operation                                                                                                              |

| Thermal Resistance6                                                                                   | Applications Information                                                                                                           |

| ESD Caution6                                                                                          | Supply Decoupling                                                                                                                  |

| Pin Configuration and Function Descriptions7                                                          | Transient Voltage Protection                                                                                                       |

| Typical Performance Characteristics9                                                                  | Typical Connection Diagrams                                                                                                        |

| Terminology12                                                                                         | Outline Dimensions                                                                                                                 |

| Theory of Operation                                                                                   | Ordering Guide                                                                                                                     |

| REVISION HISTORY                                                                                      |                                                                                                                                    |

| 12/2016—Rev. F to Rev. G                                                                              | 7/2012—Rev. A to Rev. B                                                                                                            |

| Changes to Figure 2 and Table 6                                                                       | Removed $V_{\rm CC}$ and $IOV_{\rm CC}$ Current Consumption Text, Table 2. Added Internal Oscillator and External Clock Parameters |

| 1/2014—Rev. E to Rev. F                                                                               | to Table 2                                                                                                                         |

| Changes to Figure 3 to Figure 7                                                                       | Changes to t <sub>2</sub> Description and Endnote 2, Table 3                                                                       |

| Changes to Example Section14                                                                          | Changes to IOV <sub>CC</sub> Description, Table 6                                                                                  |

| 10/2013—Rev. D to Rev. E                                                                              | Added Transient Voltage Protection Section, Figure 26, and                                                                         |

| Changes to t <sub>7</sub> and t <sub>8</sub> Descriptions, Table 35                                   | Figure 27; Renumbered Sequentially                                                                                                 |

| Changed $\theta_{JA}$ from 30°C/W to 56°C/W6                                                          | Changes to Typical Connection Diagrams Section                                                                                     |

| Added Figure 13 and Figure 1410                                                                       | Changes to Figure 29.                                                                                                              |

| Changes to External Crystal Section and Figure 2515                                                   | Changes to Figure 30                                                                                                               |

| 71044 P. G. P. P.                                                                                     | Updated Outline Dimensions                                                                                                         |

| 5/2013—Rev. C to Rev. D                                                                               | 4/2012 Pay 0 to Pay A                                                                                                              |

| 2/2013—Rev. B to Rev. C                                                                               | <b>4/2012—Rev. 0 to Rev. A</b> Change to Transmit Impedance Parameter, RTS Low, Table 2.                                           |

| Changed 2 V to 5.5 V Power Supply to 1.71 V to 5.5 V Power                                            | Changes to Figure 3, Figure 4, Figure 5, and Figure 7                                                                              |

| Supply, Features Section                                                                              | Changes to Figure 10 and Figure 11                                                                                                 |

| Changes to Summary Statement, $V_{CC}$ Parameter, and Internal                                        | Changed AD5755 to AD5755-1 Throughout                                                                                              |

| Reference Voltage Parameter Test Conditions/Comments,                                                 | · · · · · · · · · · · · · · · · · · ·                                                                                              |

| Table 2                                                                                               | Change to Figure 27                                                                                                                |

|                                                                                                       | 2/2012 Peristan 0 Letti IV                                                                                                         |

| Changed $V_{CC} = 2 \text{ V to } 5.5 \text{ V to } V_{CC} = 1.71 \text{ V to } 5.5 \text{ V in the}$ | 2/2012—Revision 0: Initial Version                                                                                                 |

| Summary Statement, Table 3                                                                            |                                                                                                                                    |

| Changes to 1 in 10 Description and ETAD Milemonic and                                                 |                                                                                                                                    |

## **SPECIFICATIONS**

$V_{CC}$  = 1.71 V to 5.5 V,  $IOV_{CC}$  = 1.71 V to 5.5 V, AGND = DGND, CLKOUT disabled, HART\_OUT with 5 nF load, internal and external receive filter, internal reference; all specifications are from -40°C to +125°C and relate to both A and B models, unless otherwise noted.

Table 2.

| Parameter <sup>1</sup>                                    | Min                   | Тур | Max                   | Unit   | Test Conditions/Comments                                                                   |

|-----------------------------------------------------------|-----------------------|-----|-----------------------|--------|--------------------------------------------------------------------------------------------|

| POWER REQUIREMENTS <sup>2</sup>                           |                       |     |                       |        |                                                                                            |

| $V_{cc}$                                                  | 1.71                  |     | 5.5                   | V      |                                                                                            |

| IOV <sub>CC</sub>                                         | 1.71                  |     | 5.5                   | V      |                                                                                            |

| V <sub>CC</sub> and IOV <sub>CC</sub> Current Consumption |                       |     |                       |        |                                                                                            |

| Demodulator                                               |                       | 86  | 115                   | μΑ     | B model, external clock, −40°C to +85°C                                                    |

|                                                           |                       |     | 179                   | μΑ     | B model, external clock, −40°C to +125°C                                                   |

|                                                           |                       | 69  | 97                    | μΑ     | B model, external clock, −40°C to +85°C, external reference                                |

|                                                           |                       |     | 157                   | μΑ     | B model, external clock, −40°C to +125°C, external reference                               |

|                                                           |                       |     | 260                   | μΑ     | A model, external clock, −40°C to +125°C                                                   |

| Modulator                                                 |                       | 124 | 140                   | μΑ     | B model, external clock, −40°C to +85°C                                                    |

|                                                           |                       |     | 193                   | μΑ     | B model, external clock, −40°C to +125°C                                                   |

|                                                           |                       | 73  | 96                    | μΑ     | B model, external clock, −40°C to +85°C, external reference                                |

|                                                           |                       |     | 153                   | μΑ     | B model, external clock, −40°C to +125°C, external reference                               |

|                                                           |                       |     | 270                   | μΑ     | A model, external clock, −40°C to +125°C                                                   |

| Crystal Oscillator <sup>3</sup>                           |                       | 33  | 60                    | μΑ     | External crystal, 16 pF at XTAL1 and XTAL2                                                 |

|                                                           |                       | 44  | 71                    | μΑ     | External crystal, 36 pF at XTAL1 and XTAL2                                                 |

| Internal Oscillator <sup>4</sup><br>Power-Down Mode       |                       | 218 | 285                   | μΑ     | AD5700-1 only, external crystal not required RESET = REF_EN = DGND                         |

|                                                           |                       | 16  | 35                    | μΑ     | Internal reference disabled, –40°C to +85°C                                                |

|                                                           |                       |     | 75                    | μA     | Internal reference disabled, –40°C to +125°C                                               |

| INTERNAL VOLTAGE REFERENCE                                |                       |     |                       | ,      |                                                                                            |

| Internal Reference Voltage                                | 1.47                  | 1.5 | 1.52                  | V      | REF_EN = $IOV_{CC}$ to enable use of internal reference; $V_{CC} = 1.71 \text{ V}$ minimum |

| Load Regulation                                           |                       | 18  |                       | ppm/μA | Tested with 50 μA load                                                                     |

| OPTIONAL EXTERNAL VOLTAGE<br>REFERENCE                    |                       |     |                       |        |                                                                                            |

| External Reference Input Voltage                          | 2.47                  | 2.5 | 2.53                  | V      | REF_EN = DGND to enable use of external reference, $V_{CC} = 2.7 \text{ V}$ minimum        |

| External Reference Input Current                          |                       |     |                       |        |                                                                                            |

| Demodulator                                               |                       | 16  | 21                    | μΑ     | Current required by external reference in receive mode                                     |

| Modulator                                                 |                       | 28  | 33                    | μΑ     | Current required by external reference in transmit mode                                    |

| Internal Oscillator                                       |                       | 5.5 | 7                     | μΑ     | Current required by external reference if using internal oscillator                        |

| Power-Down                                                |                       | 4.6 | 8.6                   | μΑ     |                                                                                            |

| DIGITAL INPUTS                                            |                       |     |                       |        |                                                                                            |

| V <sub>IH</sub> , Input High Voltage                      | $0.7 \times IOV_{CC}$ |     |                       | V      |                                                                                            |

| V <sub>IL</sub> , Input Low Voltage                       |                       |     | $0.3 \times IOV_{CC}$ | V      |                                                                                            |

| Input Current                                             | -0.1                  |     | +0.1                  | μΑ     |                                                                                            |

| Input Capacitance <sup>5</sup>                            |                       | 5   |                       | рF     | Per pin                                                                                    |

| Parameter <sup>1</sup>                | Min              | Тур    | Max    | Unit    | Test Conditions/Comments                                                                                                                               |

|---------------------------------------|------------------|--------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIGITAL OUTPUTS                       |                  |        |        |         |                                                                                                                                                        |

| V <sub>он</sub> , Output High Voltage | $IOV_{CC} - 0.5$ |        |        | V       |                                                                                                                                                        |

| V <sub>OL</sub> , Output Low Voltage  |                  |        | 0.4    | V       |                                                                                                                                                        |

| CD Assert <sup>6</sup>                | 85               | 100    | 110    | mV p-p  |                                                                                                                                                        |

| HART_IN INPUT <sup>5</sup>            |                  |        |        |         |                                                                                                                                                        |

| Input Voltage Range                   | 0                |        | REF    | V       | External reference source                                                                                                                              |

|                                       | 0                |        | 1.5    | V       | Internal reference enabled                                                                                                                             |

| HART_OUT OUTPUT                       |                  |        |        |         |                                                                                                                                                        |

| Output Voltage                        | 459              | 493    | 505    | mV p-p  | AC-coupled (2.2 $\mu$ F), measured at HART_OUT pin with 160 $\Omega$ load (worst-case load), see Figure 17 and Figure 18 for HART_OUT voltage vs. load |

| Mark Frequency <sup>7</sup>           |                  | 1200   |        | Hz      | Internal oscillator                                                                                                                                    |

| Space Frequency <sup>7</sup>          |                  | 2200   |        | Hz      | Internal oscillator                                                                                                                                    |

| Frequency Error                       | -0.5             |        | +0.5   | %       | Internal oscillator, −40°C to +85°C                                                                                                                    |

|                                       | -1               |        | +1     | %       | Internal oscillator, −40°C to +125°C                                                                                                                   |

| Phase Continuity Error <sup>5</sup>   |                  |        | 0      | Degrees |                                                                                                                                                        |

| Maximum Load Current <sup>5</sup>     |                  | 160    |        | Ω       | Worst-case load is 160 $\Omega$ , ac-coupled with 2.2 $\mu$ F, see Figure 21 for recommended configuration if driving a resistive load                 |

| Transmit Impedance                    |                  | 7      |        | Ω       | RTS low, at the HART_OUT pin                                                                                                                           |

|                                       |                  | 70     |        | kΩ      | RTS high, at the HART_OUT pin                                                                                                                          |

| INTERNAL OSCILLATOR                   |                  |        |        |         |                                                                                                                                                        |

| Frequency                             | 1.2226           | 1.2288 | 1.2349 | MHz     | –40℃ to +85℃                                                                                                                                           |

| •                                     | 1.2165           | 1.2288 | 1.2411 | MHz     | –40°C to +125°C                                                                                                                                        |

| EXTERNAL CLOCK                        |                  |        |        |         |                                                                                                                                                        |

| External Clock Source Frequency       | 3.6496           | 3.6864 | 3.7232 | MHz     |                                                                                                                                                        |

<sup>&</sup>lt;sup>1</sup>Temperature range: –40°C to +125°C; typical at 25°C.

<sup>&</sup>lt;sup>2</sup> Current consumption specifications are based on mean current values.

<sup>&</sup>lt;sup>3</sup> The demodulator and modulator currents are specified using an external clock. If using an external crystal oscillator, the crystal oscillator current specification must be added to the corresponding V<sub>CC</sub> and IOV<sub>CC</sub> demodulator/modulator current specification to obtain the total supply current required in this mode.

<sup>&</sup>lt;sup>4</sup>The demodulator and modulator currents are specified using an external clock. If using the internal oscillator, the internal oscillator current specification must be added to the corresponding V<sub>CC</sub> and IOV<sub>CC</sub> demodulator/modulator current specification to obtain the total supply current required in this mode.

<sup>&</sup>lt;sup>5</sup> Guaranteed by design and characterization, but not production tested.

<sup>&</sup>lt;sup>6</sup> Specification set assuming a sinusoidal input signal containing preamble characters at the input and an ideal external filter (see Figure 23).

<sup>7</sup> If the internal oscillator is not used, frequency accuracy is dependent on the accuracy of the crystal or clock source used.

#### **TIMING CHARACTERISTICS**

$V_{CC}$  = 1.71 V to 5.5 V,  $IOV_{CC}$  = 1.71 V to 5.5 V,  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 3.

| Parameter <sup>1</sup> | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit                       | Description                                                                                                                                                                                       |

|------------------------|----------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

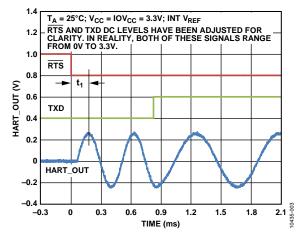

| t <sub>1</sub>         | 1                                            | Bit time <sup>2</sup> max  | Carrier start time. Time from RTS falling edge to carrier reaching its first peak. See Figure 3.                                                                                                  |

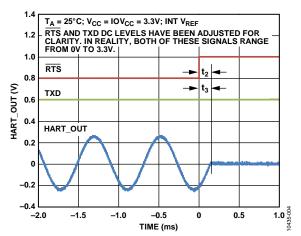

| t <sub>2</sub>         | 1                                            | Bit time <sup>2</sup> max  | Carrier stop time. Time from RTS rising edge to carrier amplitude dropping below the minimum receive amplitude.                                                                                   |

| t <sub>3</sub>         | 1                                            | Bit time <sup>2</sup> max  | Carrier decay time. Time from RTS rising edge to carrier amplitude dropping to ac zero. See Figure 4.                                                                                             |

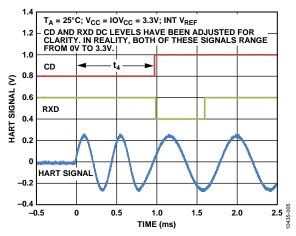

| t <sub>4</sub>         | 6                                            | Bit times <sup>2</sup> max | Carrier detect on. Time from carrier on to CD rising edge. See Figure 5.                                                                                                                          |

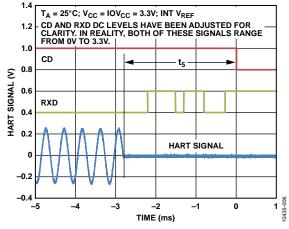

| <b>t</b> <sub>5</sub>  | 6                                            | Bit times <sup>2</sup> max | Carrier detect off. Time from carrier off to CD falling edge. See Figure 6.                                                                                                                       |

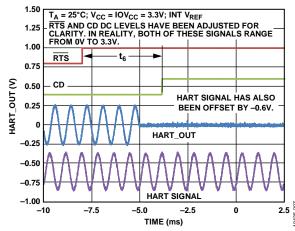

| <b>t</b> <sub>6</sub>  | 10                                           | Bit times <sup>2</sup> max | Carrier detect on when switching from transmit mode to receive mode in the presence of a constant valid carrier. Time from RTS rising edge to CD rising edge. See Figure 7.                       |

| <b>t</b> <sub>7</sub>  | 2.1                                          | ms typ                     | Crystal oscillator power-up time. On application of a valid power supply voltage at $V_{CC}$ or on enabling of the oscillator via the $\overline{XTAL\_EN}$ pin. Crystal load capacitors = 16 pF. |

| t <sub>8</sub>         | 6                                            | ms typ                     | Crystal oscillator power-up time. Crystal load capacitors = 36 pF.                                                                                                                                |

| t <sub>9</sub>         | 25                                           | μs typ                     | Internal oscillator power-up time. On application of a valid power supply voltage at $V_{\text{CC}}$ or on enabling of the oscillator via the CLK_CFG0 and CLK_CFG1 pins.                         |

| t <sub>10</sub>        | 10                                           | ms typ                     | Reference power-up time.                                                                                                                                                                          |

| t <sub>11</sub>        | 30                                           | μs typ                     | Transition time from power-down mode to normal operating mode (external clock source, external reference).                                                                                        |

$<sup>^1</sup>$  Specifications apply to AD5700/AD5700-1 configured with internal or external receive filter.  $^2$  Bit time is the length of time to transfer one bit of data (1 bit time = 1/1200 Hz = 833.333  $\mu$ s).

### ABSOLUTE MAXIMUM RATINGS

$T_A = 25$ °C, unless otherwise noted.

Transient currents of up to 100 mA do not cause SCR latch-up.

Table 4.

| Table 4.                                                 |                                                                           |

|----------------------------------------------------------|---------------------------------------------------------------------------|

| Parameter                                                | Rating                                                                    |

| V <sub>CC</sub> to GND                                   | -0.3 V to +7 V                                                            |

| IOV <sub>CC</sub> to GND                                 | −0.3 V to +7 V                                                            |

| Digital Inputs to DGND                                   | -0.3 V to IOV <sub>CC</sub> + 0.3 V or<br>+7 V (whichever is less)        |

| Digital Output to DGND                                   | -0.3 V to IOV <sub>CC</sub> + 0.3 V or<br>+7 V (whichever is less)        |

| HART_OUT to AGND                                         | −0.3 V to +2.5 V                                                          |

| HART_IN to AGND                                          | $-0.3 \text{ V to V}_{CC} + 0.3 \text{ V or}$<br>+7 V (whichever is less) |

| ADC_IP                                                   | $-0.3 \text{ V to V}_{CC} + 0.3 \text{ V or}$<br>+7 V (whichever is less) |

| AGND to DGND                                             | −0.3 V to +0.3 V                                                          |

| Operating Temperature Range (T <sub>A</sub> ) Industrial | –40°C to +125°C                                                           |

| Storage Temperature Range                                | –65℃ to +150℃                                                             |

| Junction Temperature (T <sub>J MAX</sub> )               | 150℃                                                                      |

| Power Dissipation                                        | (T <sub>J MAX</sub> – T <sub>A</sub> )/θ <sub>JA</sub>                    |

| Lead Temperature,                                        | JEDEC industry standard                                                   |

| Soldering                                                | J-STD-020                                                                 |

| ESD                                                      |                                                                           |

| Human Body Model<br>(ANSI/ESDA/JEDEC JS-001-<br>2010)    | 8 kV                                                                      |

| Field Induced Charge Model<br>(JEDEC JESD22_C101E)       | 1.5 kV                                                                    |

| Machine Model<br>(ANSI/ESD S5.2-2009)                    | 400 V                                                                     |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

Table 5. Thermal Resistance

| Package Type  | $\theta_{JA}^{1}$ | θις | Unit |

|---------------|-------------------|-----|------|

| 24-Lead LFCSP | 56                | 3   | °C/W |

<sup>&</sup>lt;sup>1</sup> Thermal impedance simulated values are based on JEDEC 2S2P thermal test board with thermal vias. See JEDEC JESD51.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

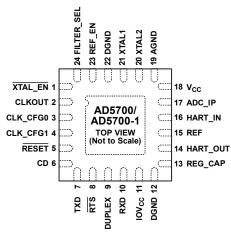

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

#### NOTES

1. THE EXPOSED PADDLE MUST BE CONNECTED

TO AGND OR DGND, OR, ALTERNATIVELY, IT CAN

BE LEFT ELECTRICALLY UNCONNECTED. IT IS

RECOMMENDED THAT THE PADDLE BE THERMALLY

CONNECTED TO A COPPER PLANE FOR ENHANCED

THERMAL PERFORMANCE.

Figure 2. Pin Configuration

**Table 6. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | XTAL_EN  | Crystal Oscillator Circuit Enable. A low state enables the crystal oscillator circuit, and an external crystal is required. A high state disables the crystal oscillator circuit, and an external clock source or the internal oscillator (AD5700-1 only) provides the clock source. This pin is used in conjunction with the CLK_CFG0 and CLK_CFG1 pins in configuring the required clock generation scheme. |

| 2       | CLKOUT   | Clock Output. If using the crystal oscillator or the internal RC oscillator, a clock output can be configured at the CLKOUT pin. Enabling the clock output consumes extra current to drive the load on this pin. See the CLKOUT section for more details.                                                                                                                                                     |

| 3       | CLK_CFG0 | Clock Configuration Control. See Table 7.                                                                                                                                                                                                                                                                                                                                                                     |

| 4       | CLK_CFG1 | Clock Configuration Control. See Table 7.                                                                                                                                                                                                                                                                                                                                                                     |

| 5       | RESET    | Active Low Digital Input. Holding RESET low places the AD5700/AD5700-1 in power-down mode. A high state on RESET returns the AD5700/AD5700-1 to their power-on state. If not using this pin, tie this pin to IOV <sub>cc</sub> .                                                                                                                                                                              |

| 6       | CD       | Carrier Detect—Digital Output. A high on CD indicates a valid carrier is detected.                                                                                                                                                                                                                                                                                                                            |

| 7       | TXD      | Transmit Data—Digital Input. Data input to the modulator.                                                                                                                                                                                                                                                                                                                                                     |

| 8       | RTS      | Request to Send—Digital Input. A high state enables the demodulator and disables the modulator. A low state enables the modulator and disables the demodulator.                                                                                                                                                                                                                                               |

| 9       | DUPLEX   | A high state on this pin enables full duplex operation. See the Theory of Operation section. A low state disables this feature.                                                                                                                                                                                                                                                                               |

| 10      | RXD      | Receive Data—UART Interface Digital Data Output. Data output from the demodulator is accessed on this pin.                                                                                                                                                                                                                                                                                                    |

| 11      | IOVcc    | Digital Interface Supply. Digital threshold levels are referenced to the voltage applied to this pin. The applied voltage can be in the range of 1.71 V to 5.5 V. $IOV_{CC}$ should be decoupled to ground with low ESR 10 $\mu$ F and 0.1 $\mu$ F capacitors (see the Supply Decoupling section).                                                                                                            |

| 12      | DGND     | Digital Circuitry Ground Reference Connection. For typical operation, it is recommended to connect this pin to AGND.                                                                                                                                                                                                                                                                                          |

| 13      | REG_CAP  | Capacitor Connection for Internal Voltage Regulator. Connect a 1 $\mu$ F capacitor from this pin to ground. Connect REG_CAP to $V_{CC}$ when $V_{CC} \le 1.98$ V.                                                                                                                                                                                                                                             |

| 14      | HART_OUT | HART FSK Signal Output. See the FSK Modulator section and Figure 30 for typical connections.                                                                                                                                                                                                                                                                                                                  |

| 15      | REF      | Internal Reference Voltage Output, or External 2.5 V Reference Voltage Input. Connect a 1 µF capacitor from this pin to ground. When supplying an external reference, the Vcc supply requires a minimum voltage of 2.7 V.                                                                                                                                                                                     |

| 16      | HART_IN  | HART FSK Signal. When using the internal filter, couple the HART input signal into this pin using a 2.2 nF series capacitor. If using an external band-pass filter as shown in Figure 23, do not connect to this pin.                                                                                                                                                                                         |

| 17      | ADC_IP   | If using the internal band-pass filter, connect 680 pF to this pin. Alternatively, this pin allows direct connection to the ADC input, in which case an external band-pass filter network must be used, as shown in Figure 23.                                                                                                                                                                                |

| Pin No. | Mnemonic        | Description                                                                                                                                                                                                                                                                                                              |

|---------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18      | V <sub>CC</sub> | Power Supply Input. 1.71 V to 5.5 V can be applied to this pin. $V_{CC}$ should be decoupled to ground with low ESR 10 $\mu$ F and 0.1 $\mu$ F capacitors (see the Supply Decoupling section).                                                                                                                           |

| 19      | AGND            | Analog Circuitry Ground Reference Connection.                                                                                                                                                                                                                                                                            |

| 20      | XTAL2           | Connection for External 3.6864 MHz Crystal. Do not connect to this pin if using the internal RC oscillator (AD5700-1 only) or an external clock source.                                                                                                                                                                  |

| 21      | XTAL1           | Connection for External 3.6864 MHz Crystal or External Clock Source Input. Tie this pin to ground if using the internal RC oscillator (AD5700-1 only).                                                                                                                                                                   |

| 22      | DGND            | Digital Circuitry Ground Reference Connection. For typical operation, it is recommended to connect this pin to AGND.                                                                                                                                                                                                     |

| 23      | REF_EN          | Reference Enable. A high state enables the internal 1.5 V reference and buffer. A low state disables the internal reference and input buffer, and a buffered external 2.5 V reference source must be applied at REF. If REF_EN is tied low, V <sub>CC</sub> must be greater than 2.7 V.                                  |

| 24      | FILTER_SEL      | Band-Pass Filter Select. A high state enables the internal filter and the HART signal should be applied to the HART_IN pin. A low state disables the internal filter and an external band-pass filter must then be connected at the ADC_IP input pin. In this case, the HART signal should be applied to the ADC_IP pin. |

| EPAD    | EPAD            | The exposed paddle must be connected to AGND or DGND, or, alternatively, it can be left electrically unconnected. It is recommended that the paddle be thermally connected to a copper plane for enhanced thermal performance.                                                                                           |

### TYPICAL PERFORMANCE CHARACTERISTICS

Figure 3. Carrier Start Time

Figure 4. Carrier Stop/Decay Time

Figure 5. Carrier Detect On Timing

Figure 6. Carrier Detect Off Timing

Figure 7. Carrier Detect on When Switching from Transmit Mode to Receive Mode in the Presence of a Constant Valid Carrier

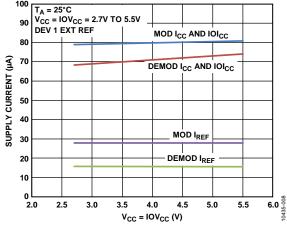

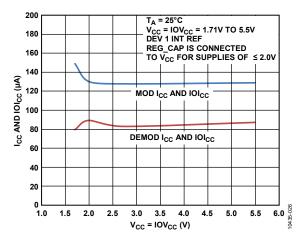

Figure 8. Supply Currents vs. Supply Voltage—External Reference

Figure 9. Supply Currents vs. Supply Voltage—Internal Reference

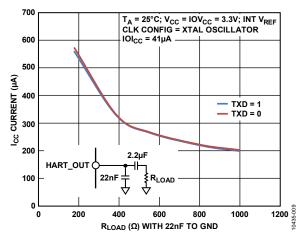

Figure 10. Current in Tx Mode vs. Resistive Load

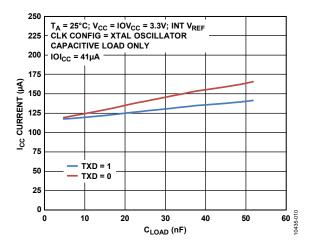

Figure 11. Current in Tx Mode vs. Capacitive Load

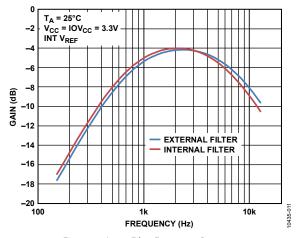

Figure 12. Input Filter Frequency Response

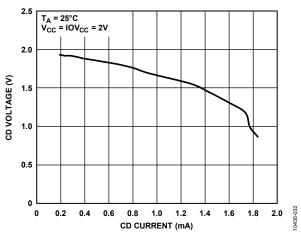

Figure 13. Carrier Detect—Voltage vs. Current, 2 V

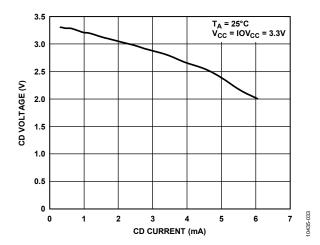

Figure 14. Carrier Detect—Voltage vs. Current, 3.3 V

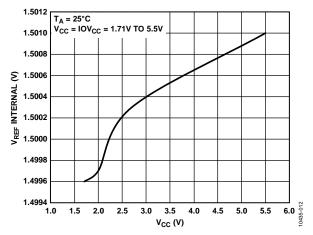

Figure 15. Reference Voltage vs. V<sub>CC</sub>

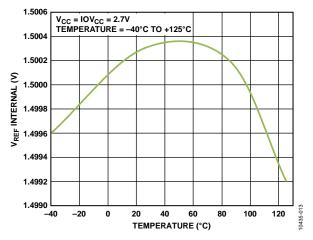

Figure 16. Reference Voltage vs. Temperature

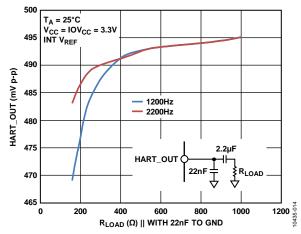

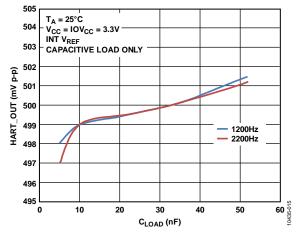

Figure 17. HART\_OUT Voltage vs. R<sub>LOAD</sub>

Figure 18. HART\_OUT Voltage vs. C<sub>LOAD</sub>

### **TERMINOLOGY**

#### $V_{\text{CC}}$ and $IOV_{\text{CC}}$ Current Consumption

This specification gives a summation of the current consumption of both the  $V_{\rm CC}$  and the  $IOV_{\rm CC}$  supplies. Figure 11 shows separate measurements for  $V_{\rm CC}$  and  $IOV_{\rm CC}$  currents vs. varying capacitive loads, in transmit mode.

#### **Load Regulation**

Load regulation is the change in reference output voltage due to a specified change in load current. It is expressed in ppm/ $\mu$ A.

#### **CD** Assert

The minimum value at which the carrier detect signal asserts is 85 mV p-p and the maximum value it asserts at is 110 mV p-p. CD is already high (asserted) for HART input signals greater than 110 mV p-p. This specification was set assuming a sinusoidal input signal containing preamble characters at the input and an ideal external filter (see Figure 23).

#### HART\_OUT Output Voltage

This is the peak-to-peak HART\_OUT output voltage. The specification in Table 2 was set using a worst-case load of 160  $\Omega$ , ac-coupled with a 2.2  $\mu F$  capacitor. Figure 17 and Figure 18 show HART\_OUT output voltages for both resistive and purely capacitive loads.

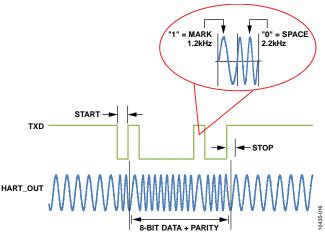

#### Mark/Space Frequency

A 1.2 kHz signal represents a digital 1, or mark, whereas a 2.2 kHz signal represents a 0, or space.

#### **Phase Continuity Error**

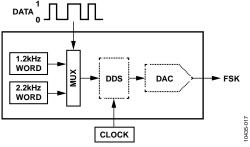

The DDS engine in this design inherently generates continuous phase signals, thus avoiding any output discontinuity when switching between frequencies. This attribute is desirable for signals that are to be transmitted over a band limited channel, because discontinuities in a signal introduce wideband frequency components. As the name suggests, for a signal to be continuous, the phase continuity error must be 0°.

### THEORY OF OPERATION

Highway Addressable Remote Transducer (HART) Communication is the global standard for sending and receiving digital information across analog wires between smart field devices and control systems. This is a digital two-way communication system, in which a 1 mA p-p frequency shift keyed (FSK) signal is modulated on top of a 4 mA to 20 mA analog current signal. The AD5700/AD5700-1 are designed and specified to operate as a single-chip, low power, HART FSK half-duplex modem, complying with the HART physical layer requirements (Revision 8.1).

A single-chip solution, the AD5700/AD5700-1 not only integrate the modulation and demodulation functions, but also contain an internal reference, an integrated receive band-pass filter (which has the flexibility of being bypassed if required), and an internally buffered HART output, giving a high output drive capability and removing the need for external buffering. The AD5700-1 option also contains a precision internal RC oscillator. The block diagram in Figure 1 shows a graphical illustration of how these circuit blocks are connected together. As a result of such extensive integration options, minimal external components are required. The AD5700/AD5700-1 are suitable for use in both HART field instrument and master configurations.

The AD5700/AD5700-1 either transmit or receive 1.2 kHz and 2.2 kHz carrier signals. A 1.2 kHz signal represents a digital 1, or mark, whereas a 2.2 kHz signal represents a 0, or space. There are three main clocking configurations supported by these parts, two of which are available on the AD5700 option, whereas all three are available on the AD5700-1 device:

- External crystal

- CMOS clock input

- Internal RC oscillator (AD5700-1 only)

The device is controlled via a standard UART interface. The relevant signals are  $\overline{RTS}$ , CD, TXD, and RXD (see Table 6 for more detail on individual pin descriptions).

#### **FSK MODULATOR**

The modulator converts a bit stream of UART-encoded HART data at the TXD input to a sequence of 1200 Hz and 2200 Hz tones (see Figure 19). This sinusoidal signal is internally buffered and output on the <u>HART\_OUT</u> pin. The modulator is enabled by bringing the <u>RTS</u> signal low.

Figure 19. AD5700/AD5700-1 Modulator Waveform

The modulator block contains a DDS engine that produces a 1.2 kHz or 2.2 kHz sine wave in digital form and then performs a digital-to-analog conversion. This DDS engine inherently generates continuous phase signals, thus avoiding any output discontinuity when switching between frequencies. For more information on DDS fundamentals, see MT-085, *Fundamentals of Direct Digital Synthesizers (DDS)*. Figure 20 demonstrates a simple implementation of this FSK encoding.

Figure 20. DDS-Based FSK Encoder

#### **CONNECTING TO HART OUT**

The HART\_OUT pin is dc biased to 0.75 V and should be capacitively coupled to the load. The current consumption specifications in Table 2 are based on driving a 5 nF load. If the application requires a larger load value, more current is required. This value can be calculated from the following formula:

$$I_{\mathit{TOTAL}} = I_{\mathit{AD5700}} + I_{\mathit{LOAD\ RMS}}$$

$$I_{LOAD RMS} = \frac{500 \text{ mV}}{4\sqrt{2} \times \sqrt{\left(\frac{1}{2\pi \times f \times C_{LOAD}}\right)^2 + R_{LOAD}^2}}$$

(1)

where:

$I_{AD5700}$  is the current drawn by the AD5700/AD5700-1 in transmit mode as per specifications (see Table 2). Note that the specifications in Table 2 assume a 5 nF  $C_{LOAD}$ .

*f* is the output frequency (1.2 kHz or 2.2 kHz).

$C_{LOAD}$  is the capacitive load to ground on HART\_OUT.

$R_{LOAD}$  is the resistive load on the loop.

When driving a purely capacitive load, the load should be in the range of 5 nF to 52 nF. See Figure 11 for a typical plot of supply current vs. capacitive load.

#### Example

Assume use of an internal reference, and  $C_{LOAD} = 52 \text{ nF}$ .

$I_{CC} + IOI_{CC} = 140 \,\mu\text{A}$  maximum (from Table 2 specification)

Note that this is incorporating a 5 nF load.

Therefore, to calculate the load current required to drive the extra 47 nF, use Equation 1.

Substituting f = 1200 Hz,  $C_{LOAD}$  = 47 nF, and  $R_{LOAD}$  = 0  $\Omega$  into the formula results in  $I_{LOAD}$  of 31.3  $\mu A$ .

If using the crystal oscillator, this adds  $60 \,\mu\text{A}$  maximum (see Table 2 for conditions).

Thus, the total worst-case current in this example is:

$$140 \mu A + 31.3 \mu A + 60 \mu A = 231.3 \mu A$$

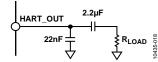

If driving a load with a resistive element, it is recommended to place a 22 nF capacitor to ground at the HART\_OUT pin. The load should be coupled with a 2.2  $\mu F$  series capacitor. For low impedance devices, the  $R_{LOAD}$  range is typically 230  $\Omega$  to 600  $\Omega$ .

Figure 21. AD5700/AD5700-1 with Resistive Load at HART OUT

#### **FSK DEMODULATOR**

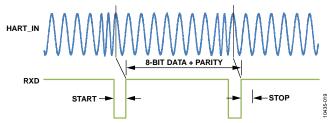

Figure 22. AD5700/AD5700-1 Demodulator Waveform (Preamble Message 0xFF)

When RTS is logic high, the modulator is disabled and the demodulator is enabled, that is, the AD5700/AD5700-1 are in receive mode. A high on CD indicates a valid carrier is detected. The demodulator accepts an FSK signal at the HART\_IN pin and restores the original modulated signal at the UART interface digital data output pin, RXD. The combination of the ADC, digital filtering and digital demodulation results in a highly accurate output on the RXD pin. The HART bit stream follows a standard UART frame with a start bit, 8-bit data, one parity, and a stop bit (see Figure 22).

### CONNECTING TO HART\_IN OR ADC IP

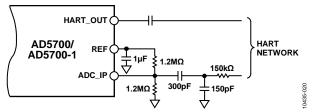

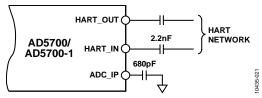

The AD5700/AD5700-1 have two filter configuration options: an external filter (HART signal is applied to ACP\_IP) and an internal filter (HART signal is applied to HART\_IN).

The external filter configuration is shown in Figure 23. In this case, the HART signal is applied to the ADC\_IP pin through an external filter circuit. In safety critical applications, the AD5700/AD5700-1 must be isolated from the high voltage of the loop supply. The recommended external band-pass filter includes a  $150~\rm k\Omega$  resistor, which limits current to a sufficiently low level to adhere to intrinsic safety requirements. In this case, the input has higher transient voltage protection and should, therefore, not require additional protection circuitry, even in the most demanding of industrial environments. Assuming the use of a 1% accurate resistor and 10% accurate capacitor components, the calculated variation in CD trip voltage levels vs. the ideal is  $\pm 3.5~\rm mV$ .

Figure 23. AD5700/AD5700-1 with External Filter on ADC\_IP

The internal filter configuration is shown in Figure 24. This option is beneficial where cost or board space is a large concern because it removes the need for multiple external components. This configuration achieves an 8 kV ESD HBM rating but requires extra external protection circuitry for EMC and surge protection purposes if used in harsh industrial environments.

Figure 24. AD5700/AD5700-1 Using Internal Filter on HART\_IN

#### **CLOCK CONFIGURATION**

The AD5700/AD5700-1 support numerous clocking configurations to allow the optimal trade-off between cost and power:

- External crystal

- CMOS clock input

- Internal RC oscillator (AD5700-1 only)

The CLK\_CFG0, CLK\_CFG1, and XTAL\_EN pins configure the clock generation as shown in Table 7. The AD5700/AD5700-1 can also provide a clock output at CLKOUT (for more details, see the CLKOUT section).

#### **External Crystal**

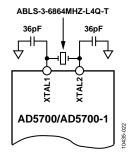

The typical connection for an external crystal (ABLS-3.6864MHZ-L4Q-T) is shown in Figure 25. To ensure minimum current consumption and to minimize stray capacitances, connections between the crystal, capacitors, and ground should be made as close to the AD5700/AD5700-1 as possible. Consult individual crystal vendors for recommended load information and crystal performance specifications.

Figure 25. Crystal Oscillator Connection

The ABLS-3.6864MHZ-IAQ-T crystal oscillator data sheet recommended two 36 pF capacitors. Because the crystal current consumption is dominated by the load capacitance, in an effort to reduce the crystal current consumption, two 16 pF capacitors were used on the XTAL1 and XTAL2 pins. The AD5700/AD5700-1 still functioned as expected, even with the resulting reduction in frequency performance from the crystal due to the smaller capacitance values. Crystals are available that support 16 pF capacitors. It is recommended to consult the relevant crystal manufacturers for this information.

#### **CMOS Clock Input**

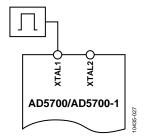

A CMOS clock input can also be used to generate a clock for the AD5700/AD5700-1. To use this mode, connect an external clock source to the XTAL 1 pin, and leave XTAL2 open circuit (see Figure 26).

Figure 26. CMOS Clock Connection

#### Internal Oscillator (AD5700-1 only)

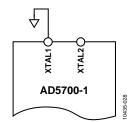

Consuming typically 218  $\mu$ A, the low power, internal, 0.5 % precision RC oscillator, available only on the AD5700-1, has an oscillation frequency of 1.2288 MHz. To use this mode, tie the XTAL1 pin to ground and leave the XTAL2 pin open circuit (see Figure 27).

Figure 27. Internal Oscillator Connection

#### **CLKOUT**

The AD5700/AD5700-1 can provide a clock output at CLKOUT (see Table 7).

- If using the crystal oscillator, this clock output can be configured as a 3.6864 MHz, 1.8432 MHz, or 1.2288 MHz buffer clock.

- If using a CMOS clock, no clock output can be configured at the CLKOUT pin.

- If using the internal RC oscillator, this clock output is only available as a 1.2288 MHz buffer clock.

The amplitude of the clock output depends on the  $IOV_{CC}$  level; therefore, the clock output can be in the range of 1.71 V p-p to 5.5 V p-p. Enabling the clock output of the AD5700/AD5700-1 increases the current consumption of the device. This increase is due to the current required to drive any load at the CLKOUT pin, which should not be more than 30 pF.

This capacitance should be minimized to reduce current consumption and provide the clock with the cleanest edges. The additional current drawn from the  $IOV_{CC}$  supply can be calculated using the following equation:

$$I = C \times V \times f$$

| Table 7. Clock Con | ıfiguration | <b>Options</b> |

|--------------------|-------------|----------------|

|--------------------|-------------|----------------|

| XTAL_EN | CLK_CFG1 | CLK_CFG0 | CLKOUT            | Description                                                 |

|---------|----------|----------|-------------------|-------------------------------------------------------------|

| 1       | 0        | 0        | No output         | 3.6864 MHz CMOS clock connected at XTAL1 pin                |

| 1       | 0        | 1        | No output         | 1.2288 MHz CMOS clock connected at XTAL1 pin                |

| 1       | 1        | 0        | No output         | Internal oscillator enabled (AD5700-1 only)                 |

| 1       | 1        | 1        | 1.2288 MHz output | Internal oscillator enabled, CLKOUT enabled (AD5700-1 only) |

| 0       | 0        | 0        | No output         | Crystal oscillator enabled                                  |

| 0       | 0        | 1        | 3.6864 MHz output | Crystal oscillator enabled, CLKOUT enabled                  |

| 0       | 1        | 0        | 1.8432 MHz output | Crystal oscillator enabled, CLKOUT enabled                  |

| 0       | 1        | 1        | 1.2288 MHz output | Crystal oscillator enabled, CLKOUT enabled                  |

#### **SUPPLY CURRENT CALCULATIONS**

The  $V_{CC}$  and  $IOV_{CC}$  current consumption specifications shown in Table 2 are derived using the internal reference and an external clock source. This specification is given for a maximum temperature of  $85^{\circ}C$  (115  $\mu A$  receive current and 140  $\mu A$  transmit current) and an extended maximum temperature of  $125^{\circ}C$  (179  $\mu A$  receive current and 193  $\mu A$  transmit current). Alternatively, if the external reference is preferred, (assuming a maximum temperature of  $85^{\circ}C$ ), the receive and transmit supply current values become  $118~\mu A$  and  $129~\mu A$  respectively, including the current required by the external reference. A similar calculation can be done for the  $125^{\circ}C$  maximum temperature case.

If the crystal oscillator or internal oscillator is used,  $V_{\rm CC}$  and  $IOV_{\rm CC}$  current consumption figures return to the 115  $\mu A$  receive current and 140  $\mu A$  transmit current. However, the resultant current consumption from the crystal oscillator or internal oscillator must now be accounted for, 60  $\mu A$  maximum additional current for the crystal oscillator, or 285  $\mu A$  maximum additional current for the internal oscillator option. This gives a maximum current consumption of 175  $\mu A$  in receive mode and 200  $\mu A$  in transmit mode, when using the internal reference and the crystal oscillator. Utilizing the internal reference and the internal oscillator (AD5700-1 only) results in a total maximum current consumption of 400  $\mu A$  for receive current and 425  $\mu A$  for transmit current.

#### **POWER-DOWN MODE**

The AD5700/AD5700-1 can be placed into power-down mode by holding the RESET pin low. If using the internal reference, it is recommended to tie the REF\_EN pin to the RESET pin so that it is also powered down. If the reference is not powered down while RESET is low, the output voltage on the REF pin is approximately 1.7 V until RESET is brought high again.

In this mode, the receive, transmit, and oscillator circuits are all switched off, and the device consumes a typical current of  $16 \mu A$ .

#### **FULL DUPLEX OPERATION**

Full duplex operation means that the modulator and demodulator of the AD5700/AD5700-1 are enabled at the same time. This is a powerful feature, enabling a self-test procedure of not only the HART device but also the complete signal path between the HART device and the host controller. This provides verification that the local communications loop is functional. This increased level of system diagnostics is useful in production self-test and is advantageous in improving the application's safety integrity level (SIL) rating. The full duplex mode of operation is enabled by connecting the DUPLEX pin to logic high.

### APPLICATIONS INFORMATION

#### **SUPPLY DECOUPLING**

It is recommended to decouple the  $V_{CC}$  and  $IOV_{CC}$  supplies with  $10~\mu F$  in parallel with  $0.1~\mu F$  capacitors to ground. For many applications,  $1~\mu F$  in parallel with  $0.1~\mu F$  ceramic capacitors to ground should be sufficient. The REG\_CAP voltage of 1.8~V is used to supply the AD5700/AD5700-1 internal circuitry and is derived from the  $V_{CC}$  supply using a high efficiency clocking LDO. Decouple this REG\_CAP supply with a  $1~\mu F$  ceramic capacitor to ground. It is also required to decouple the REF pin with a  $1~\mu F$  ceramic capacitor to ground. Place decoupling capacitors as close to the relevant pins as possible.

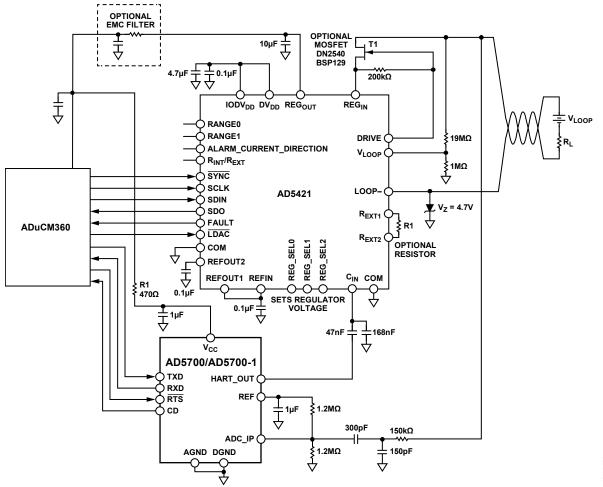

For loop-powered applications, it is recommended to connect a resistance in series with the  $V_{\rm CC}$  supply to minimize the effect of any noise, which may, depending on the system configuration, be introduced onto the loop as a result of current draw variations from the AD5700/AD5700-1. For typical applications, 470  $\Omega$  of resistance has proven most effective. However, depending on the application conditions, alternative values may also be acceptable (see R1 in Figure 31).

#### TRANSIENT VOLTAGE PROTECTION

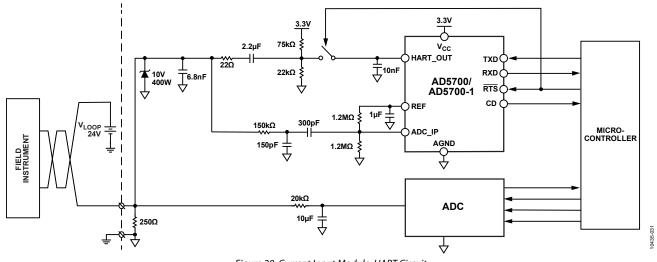

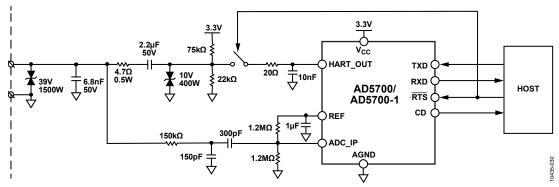

Many industrial control applications have requirements for HART-enabled current input and output modules. Figure 28

shows an example of a HART-enabled current input module that contains transient voltage protection circuitry, which is very important in harsh industrial control environments.

The module is powered from a 24 V field supply, and the 250  $\Omega$ load is within the low impedance module itself. This configuration is in contrast to Figure 29, which demonstrates a secondary HART device, in which the load is outside of the module. For transient voltage protection, a 10 V unidirectional (for protection against positive high voltage transients) transient voltage suppressor (TVS) is placed at the connection point of the current input module. The TVS component that is used in a given application circuit must have power ratings that are appropriate to the individual system. When choosing the TVS, low leakage current is also an important specification for maintaining the accuracy of the analog current input. In the event of a transient spike, the 22  $\Omega$  series resistor acts as a current limiting resistor for the FSK output pin. The FSK input pin is inherently protected by the 150 k $\Omega$  resistor, which forms part of the recommended external filter circuitry at the FSK input. The voltage divider, made up of both a 75 k $\Omega$ resistor and a 22 k $\Omega$  resistor, is used to maintain a 0.75 V dc bias at the field side of the FSK output switch.

Figure 28. Current Input Module, HART Circuit

Figure 29. Secondary HART Device

Rev. G | Page 17 of 24

As previously mentioned, Figure 29 shows an example secondary HART device, incorporating two-stage protection circuitry. In this example, a bidirectional (for protection against both positive and negative high voltage transients) TVS is included to provide flexibility in the polarity of the connection points of the module. Because this module could be connected to any point on the current loop, the higher TVS rating was chosen. The lower rated second stage provides added protection for the AD5700/AD5700-1 device.

#### TYPICAL CONNECTION DIAGRAMS

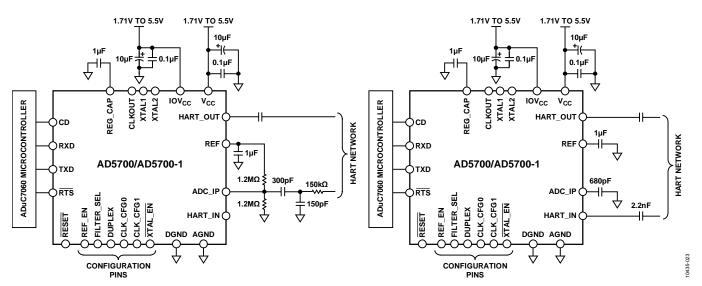

Figure 30 shows a typical connection diagram for the AD5700/AD5700-1 using the external and internal options. See the Connecting to HART\_IN or ADC\_IP section for more details.

The AD5700/AD5700-1 are designed to interface easily with Analog Devices, Inc., innovative portfolio of industrial converters like the AD5421 loop-powered current-output DAC, the AD5410/AD5420 and AD5412/AD5422 family of line-powered current-output DACs, and the AD5755-1, a quad DAC with innovative dynamic power control technology. The

combination of Analog Devices industrial converters and the AD5700/AD5700-1 greatly simplifies system design, enhancing reliability while reducing overall PCB size.

Figure 31 shows how the AD5700/AD5700-1 HART modem can be interfaced with the AD5421 (4 mA to 20 mA loop-powered DAC) and the ADuCM360 microcontroller to construct a loop powered transmitter circuit. The HART signal from HART\_OUT is introduced to the AD5421 via the  $C_{\rm IN}$  pin.

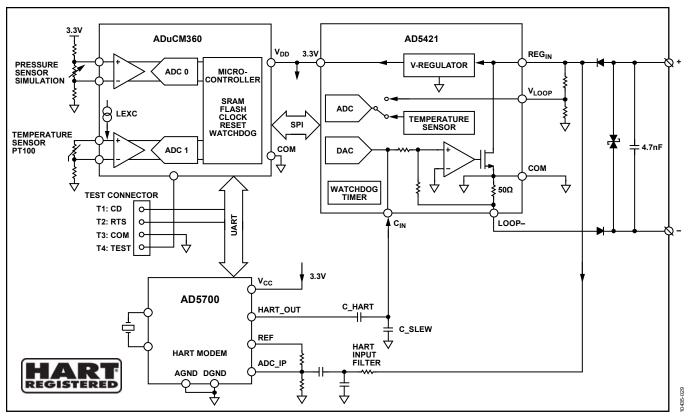

The HART enabled smart transmitter reference demo circuit (the block diagram shown in Figure 32) was developed by Analog Devices and uses the AD5421, a 16-bit, loop-powered, 4 mA to 20 mA DAC, the ADuCM360 microcontroller and the AD5700 modem. This circuit has been compliance tested, verified, and registered as an approved HART solution by the HART Communication Foundation. Contact your sales representative for further information about this demo circuit.

In conclusion, the AD5700/AD5700-1 enable quick and easy deployment of a robust HART-compliant system.

Figure 30. AD5700/AD5700-1 Typical Connection Diagram for External and Internal Filter Options

Figure 31. Loop-Powered Transmitter Diagram

Figure 32. Block Diagram—Analog Devices HART-Enabled Smart Transmitter Reference Demo Circuit

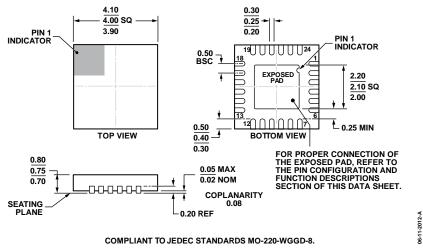

### **OUTLINE DIMENSIONS**

Figure 33. 24-Lead Lead Frame Chip Scale Package [LFCSP\_WQ] 4 mm × 4 mm Body, Very Thin Quad (CP-24-10) Dimensions shown in millimeters

#### **ORDERING GUIDE**

|                    |                   |                                                | Receive Supply |                                          | Package  |

|--------------------|-------------------|------------------------------------------------|----------------|------------------------------------------|----------|

| Model <sup>1</sup> | Temperature Range | Oscillator Options                             | Current        | Package Description                      | Option   |

| AD5700BCPZ-R5      | –40℃ to +125℃     | External clock, crystal                        | 157 μΑ         | 24-Lead LFCSP_WQ                         | CP-24-10 |

| AD5700BCPZ-RL7     | –40°C to +125°C   | External clock, crystal                        | 157 μΑ         | 24-Lead LFCSP_WQ                         | CP-24-10 |

| AD5700ACPZ-RL7     | –40°C to +125°C   | External clock, crystal                        | 260 μΑ         | 24-Lead LFCSP_WQ                         | CP-24-10 |

| AD5700-1BCPZ-R5    | –40°C to +125°C   | External clock, crystal or internal oscillator | 442 μΑ         | 24-Lead LFCSP_WQ                         | CP-24-10 |

| AD5700-1BCPZ-RL7   | –40℃ to +125℃     | External clock, crystal or internal oscillator | 442 μΑ         | 24-Lead LFCSP_WQ                         | CP-24-10 |

| AD5700-1ACPZ-RL7   | –40℃ to +125℃     | External clock, crystal or internal oscillator | 540 μΑ         | 24-Lead LFCSP_WQ                         | CP-24-10 |

| EVAL-AD5700-1EBZ   |                   |                                                |                | Evaluation Board for AD5700 and AD5700-1 |          |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

## NOTES

## NOTES

**NOTES**

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

AD5700-1ACPZ-RL7 AD5700-1BCPZ-R5 AD5700-1BCPZ-RL7 EVAL-AD5700-1EBZ